PLL-Frequenzsynthese: Spezielles Problem mit dem

CD4046B (MC14046B) und 74HC4046

(-> Self-Bias-Circuit)

- Elektronik-Minikurse: Inhaltsverzeichnis WICHTIG: Diverse technische Infos

- Elektronik-Minikurse: Philosophie (Sinn, Vorwissen, Praxisbezug)

- Hilfe bei Leserfragen. (WICHTIG: Unbedingt zur Kenntnis nehmen!)

- Simulieren und Experimentieren, ein Vorwort von Jochen Zilg

- Autor: Thomas Schaerer Opamp-Buch Timer555-Buch

Dieses Foto zeigt einen fast perfekten PLL-Frequenzmultiplier, bestehend aus einem CMOS-PLL-IC des Typs CD4046B (MC14046B) oder 74HC4046, einem passiven Loop-Tiefpassfilter, einem Feedbackfrequenzteiler des Typs CD4040B (MC14040B) oder 74HC4040 und einem als Schmitt-Trigger arbeitenden LMC555-Timer (CMOS-Version) auf einem Testboard. Weshalb nur fast perfekt, beschreibt der vorliegende Bericht...

Die Voraussetzung

Zum vollständigen Verständnis setzt dieser Elektronik-Minikurs voraus, dass der Leser weiss, wie eine digitale Phase-Locked-Loop-Schaltung (PLL-Schaltung) funktioniert. Grundlagenwissen wird dazu nicht vermittelt. Empfehlenswerte Bücher sind "Theorie und Anwendungen des Phase-locked Loops" von Roland Best (ISBN: 3-85502-132-5) und "Halbleiter-Schaltungs-Technik" von Tietze/Schenk. "Das CMOS-Kochbuch" von Don Lancaster bietet ebenso, jedoch nur eine bescheidene aber durchaus praktikable Einführung in die Welt des PLL. Es gibt von mir ein spezieller Elektronik-Minikurs der zum PLL-Thema passt:

Im vorliegenden Artikel geht es einzig darum eine wichtige Schwachstelle der PLL-Bausteine CD4046B (MC14046B) und 74HC4046 zu fokussieren und dies soll dazu dienen, dass andere Schaltungsentwickler nicht die selbe Erfahrung machen und unnötig Zeit in die Fehlersuche investieren müssen. CD4046B von National Seminconductor Corporation (NSC) und MC14046B von Motorola sind elektronisch identisch. 74HC4046 ist die HCMOS-Version. Wenn alle drei Typen angesprochen sind, werde ich nur noch den 4046 erwähnen.

Definition der Betriebsspannung

In den Datenblättern der CMOS-Logik der Serie MC140xx oder CD40xx werden die Betriebsspannungen mit VDD und VSS angegeben. In den Datenblättern der HCMOS-Logik 74HCxxxx jedoch mit Vcc und GND, wie dies bei der bipolaren TTL-Logik üblich ist. Dies ist schon deshalb verständlich, weil die HC- und HCTMOS-Logik ursprünglich entwickelt wurde, um die TTL-Logik zu ersetzen, wo dies durch die Taktfrequenz möglich ist. Die HCTMOS-Logik dient als Schnittstelle zwichen der TTL- und HCMOS-Welt (TTL-Ausgang --> HCTMOS-Eingang). Nichts desto trotz ist es aber auch mit der HCMOS-Logik möglich, die ICs mit symmetrischer Betriebsspannung, z.B. mit ± 2.5 VDC, zu betreiben, was oft bei analog-digitaler Mischschaltung Sinn macht. Dies bedeutet, dass der vermeintliche GND-Anschluss eben auch an eine negative Spannung angeschlossen werden kann. Ich werde in diesem Kurs alle Speiseanschlüsse, gleichgültig ob CMOS oder HCMOS, mit Vcc und GND bezeichnen, da betreffs der Störungsbeschreibung des 4046 sowohl CMOS als auch HCMOS gemeint sind.

Die PLL-Schaltung mit dem 4046

Bild 1 zeigt wie der 4046 grundsätzlich beschaltet wird. Dieses

IC enthält drei Phasendiskriminatoren, die man auch Phasenvergleicher,

bzw. Phasenkomparatoren, bezeichnet. Sie haben einen gemeinsamen

Signaleingang (Pin 14) und einen gemeinsamen Komparatoreingang (Pin 3).

Im Beispiel von Bild 1 wird der Komparatortyp II (Pin 13) verwendet. Er

hat gegenüber Komparatortyp I den Vorteil, dass der PLL nicht auf die

Harmonischen der Referenzfrequenz (Pin 14) einrasten kann. Dies erlaubt

den PLL in einem grossen Frequenzbereich (grosser Fangbereich)

einzusetzen. Dies hat dafür den Nachteil, dass er schlechter das

Rauschen des Eingangsignales an Pin 14 unterdrückt. Dies kann der

Phasenkomparator I, der bloss aus einer EXOR-Schaltung besteht, besser,

jedoch rastet die PLL mit ihm auch auf Harmonische der Eingangsfrequenz

an Pin 14 ein. Zwei der drei Komparatoren sind in Bild 2 etwas

differenzierter dargestellt.

In Bild 1 folgt auf den Phasenkomparator II das passive

Loop-Tiefpassfilter, das hier ebenso nur angedeutet wird wie der

darauffolgende spannungsgesteuerte Oszillator, der VCO (Voltage

Controlled Oscillator). Sein Ausgangssignal führt über einen

Frequenzteiler (Divider 1/n) zurück zum Phasenkomparator. Dort werden

die beiden Phasen an den Eingänge miteinander verglichen und über das

Loop-Tiefpassfilter erhält der VCO-Eingang die korrekte Gleichspannung,

damit es zur exakten Frequenzmultiplikation f*n kommt. Damit ist

Regelfunktion erklärt.

Im Weiteren fokussieren wir den Sektor des Phasenkomparators, besser

gesagt, auf ein kleines aber wichtiges Detail von ihm, das ab Bild 2

thematisiert wird.

Weshalb nur fast perfekt?

Ein PLL-Regelkreis mit dem Phasenkomparator II, wie eben kurz

beschrieben, funktioniert perfekt stabil, mit geringem Phasenjitter und

kurzer Einschwingdauer nach Frequenzänderungen, wenn das

Loop-Tiefpassfilter und der Spannungshub des VCO richtig dimensioniert

sind. Der Umgang mit diesem IC ist recht einfach. Diese Erfahrung werden

sicher schon viele Schaltungsentwickler gemacht haben. Allerdings haben

manche kaum bemerkt, dass es im 4046 eine Schwachstelle gibt,

wenn das Eingangssignal an Pin 14 in Amplitude und Flankensteilheit

gerade noch Werte enthalten, so dass die Störung, von der gleich die

Rede sein wird, noch nicht auftreten kann. Bild 2 deutet den Problemfall

an. Der Sündenbock ist der Self-Biasing-Amplifier.

Die Phasenkomparatoren I und II benötigen digitale Signale. Beim Eingang

an Pin 3 ist dies in der Regel "automatisch" garantiert, weil er

entweder direkt vom VCO-Ausgang oder von einem einem

Frequenzteiler-Ausgang gesteuert wird. Auf den Eingang von Pin 14, der

als Signal-Input bezeichnet wird, ist das etwas anders. Gemäss

Datenblatt folgt auf diesen Eingang ein sogenannter

Self-Biasing-Amplifier. Die Frage ist natürlich was dieser mit dem

Eingangssignal anstellt? Das Datenblatt der CMOS-Version erlaubt

Eingangsspannungen mit typischen Werten zwischen 200 mV bis 700 mV, im

Bereich einer Betriebsspannung zwischen 5 VDC und 15 VDC, bei einer

Frequenz von 50 kHz, wenn man in Serie zum Eingang einen Kondensator von

1000 pF schaltet. Dieser Kondensator bildet mit dem Eingangswiderstand,

der typisch zwischen 2 M-Ohm und 200 k-Ohm im Bereich einer

Betriebsspannung zwischen 5 VDC und 15 VDC liegt, ein passives

Hochpassfilter erster Ordnung. Dazu kommt, dass die DC-Entkopplung durch

den Kondensator den Self-Biasing-Ampilifier in die Lage versetzt, den

Eingang auf die halbe Betriebsspannung zu justieren. Eine wichtige

Voraussetzung für die Triggerung mit kleinen Impulsamplituden.

Die Datenblätter von NSC und Motorola beschreiben diesen Spezialfall

unterschiedlich. Motorola schreibt bloss: The signal-input can be

directly coupled for a large voltage signal, or a capacitively coupled

to the self-biasing amplifier at the signal input for a small voltage

signal.

Fairchild und NSC gehen mehr ins Detail, jedoch nur bei der

HCMOS-Version 74HC4046. Das "Innenleben" des Self-Biasing-Amplifier

zeigt sich transparenter. Man kann allerdings davon ausgehen, dass die

Schaltung des MC14046 (CD4046) und des 74HC4046 prinzipiell gleich

aufgebaut ist. Es stellte sich bei der Untersuchung auch heraus, dass

die CMOS- und die HCMOS-Version das selbe Symptom aufweist. Das nächste

Kapitel beschreibt dieses Symptom.

Verbotenes und Erlaubtes

Wer glaubt, es genüge mit einer niedrigen sinusförmigen Signalfrequenz

am Signal-Eingang Pin 14 - z.B. mit 50 Hz zwecks

Netzfrequenzsynchronisation - zu arbeiten, wie dies das Datenblatt

suggeriert, fällt sogleich auf die Nase. Es funktioniert auch dann

nicht, wenn eine grosse Signalamplitude vorliegt. Es funktioniert selbst

dann nicht befriedigend wenn der Signal-Eingang derart übersteuert wird,

dass die Sinusspannung zu einer Trapezspannung "mutiert". Der PLL rastet

nicht sauber und stabil ein. Es ist dabei irrelevant ob der

Signaleingang direkt oder kapazitiv gekoppelt ist. Wichtig ist einzig

die Amplitudensymmetrie um den halben Betriebsspannungswert. Wie diese

realisiert wird ist ebenfalls irrelevant. Fazit: Man muss selbst dafür

sorgen, dass der Signal-Eingang an Pin 14 ein Signal mit steilen

Flanken, wie es sich für digitale Signale gehört, bekommt. Nur dann

rastet der PLL problemlos ein und arbeitet stabil. Naja, stimmt das auch

wirklich?

Die typische Radio-Eriwan-Antwort lautet: "Im Prinzip ja, aber...", und

diese kommt hier auch zur Anwendung. Dazu zitiere ich nochmal den

"aufschlussreichen" Satz aus dem Datenblatt: The signal-input can

be directly coupled for a large voltage signal, or a capacitively

coupled to the self-biasing amplifier at the signal input for a small

voltage signal.

Da steht also, dass das Eingangssignal klein und gross sein darf. Hat

man einmal dafür gesorgt, dass das Eingangssignal steilflankig ist,

sollte der PLL mit einem grossen Eingangsamplitudenbereich perfekt

arbeiten. Mit dem minimalen Eingangsspannungswert arbeitet die PLL

gemäss Datenblatt gerade noch. Wer aber glaubt, gross bedeutet eine

Amplitude entsprechend der Betriebsspannung, wie dies bei CMOS üblich

ist, der irrt! Das Gemeine ist allerdings, man merkt es nicht gleich und

man kann viel Zeit mit der Fehlersuche verbringen, da der Fehler nur

sporadisch auftritt. Dies geschah mir und genau dies war die Motivation

diesen Artikel zu schreiben, der verhindern soll, dass andere sich

ebenfalls erst die Haare rauffen müssen, bis sie den Fehler gefunden

haben. Man beachte zunächst Bild 3, das zeigt, welche

Eingangsamplitudenwerte verboten und was erlaubt ist.

Die Teilbilder 3.1 und 3.2 zeigen ein Eingangssignal mit geringer Flankensteilheit, dargestellt als Dreiecksignal. Dieses Signal kann eine Spannung haben, wie im Datenblatt empfohlen, bis hin zum Maximalwert zwischen Vcc und GND, wobei man das Signal auch übersteuern (clippen) darf, - z.B. durch Begrenzung mit Kleinsignal-Siliziumdioden. Der PLL rastet in jedem Fall nicht stabil ein. Daher sind solche Signale nutzlos! Einzig Teilbild 3.3 zeigt das korrekte Eingangssignal, falls es grösser ist als die minimal geforderte Spannung, gemäss Datenblatt. Das Signal muss aber keineswegs ein symmetrisches Tastverhältnis haben wenn der Phasenkomparator II benutzt wird. Einzig steile Flanken zählen! Ein Rechtecksignal mit einer Amplitude zwischen Vcc und GND (Bild 3.4) ist allerdings zu unterlassen. Aber warum, wird sich der Leser fragen...

Im Falle von Bild 3.4, so wie es in CMOS-Logikschaltungen üblich ist, arbeitet der PLL lange Zeit problemlos, doch plötzlich rastet er kurzfristig aus und sogleich wieder ein. Es kann einige Minuten bis eine halbe Stunde oder auch mal länger dauern bis er wieder ausrastet. Manchmal aber gleich zweimal hintereinander.

Man kann sich lebhaft vorstellen, wie aufregend die Sucherei ist, wenn

der Fehler nur derart selten in Erscheinung tritt, und alle Teile in

einem geschlossenen Regelkreis voneinander abhängig sind. Ich tippte

erstmal auf externe Störsignale, welche von aussen über die

Speiseleitung, über den Signalgenerator oder aber auch über die

Messleitung des Oszilloskopen oder Frequenzzähler einwirkten. Ich konnte

dies zwar kaum glauben, aber die Art und Weise wie diese Störung

auftrat, liess erst einmal den Gadanken an eine äussere Störquelle

aufkeimen. Ich machte dann versuchsweise alles was möglich war

niederohmiger, auch das Loop-Tiefpassfilter, - natürlich bei den selben

Zeitkonstanten. Auch das brachte nichts. Dann habe ich mal den

COMBISCOPE-Oszilloskopen PM3394A von analog auf digital umgeschaltet und

ich beobachtete akribisch das Feedbackeingangssignal an Pin 3 des

Phasenkomparators. Ich dehnte dabei die Zeitablenkung massiv, so dass

man den Phasenjitter gut beobachten konnte, der solange die PLL

eingerastet war, erwartungsgemäss sehr gering ist. Aber da beobachtete

ich ganz selten vereinzelte Phasenjitterereignisse die z.T. besonders

gross waren und einige Male passierte es, dass der PLL dabei ausrastete.

Damit verstand ich aber noch immer nicht warum dies passiert. Ich

studierte zunächst einmal lange um diese ganze Problematik herum und

dachte, was denn bloss die Ursache sein könnte.

Ursprünglich realiserte ich die Schaltung mit der CMOS-Version, also mit

dem MC14046B oder CD4046B und so beachtete ich das Datenblatt der

HCMOS-Version 74HC4046 nicht. Also wusste ich auch nichts über das

Innenleben des Self-Biasing-Amplifier. Ich überlegte,

wie sich wohl ein Operationsverstärker verhalten könnte, falls der

Self-Biasing-Amplifier daraus bestehen würde. Ich dachte an die

bekannten Inversionseffekte: Bei Übersteuerung des nichtinvertierenden

Eingangs invertiert plötzlich die Ausgangspannung. Dies würde

natürlich die Störung erklären und sie tritt eben dann selten auf,

wenn die Übersteuerung nur ganz knapp erreicht würde. Ein

Leser machte mich einestages darauf aufmerksam, dass ich das

Datenblatt des 74HC4046 einmal näher betrachten solle, weil dort der

Self-Biasing-Amplifier detailliert dargestellt ist. Meine

Operationsverstärkerthoerie löste sich rasch ins Nichts auf und ich

untersuchte die Angelegenheit von Neuem, denn der beschriebene Störfall

bleibt Tatsache und ich ging davon aus, dass der Self-Biasing-Amplifier

in der CMOS- und HCMOS-Version gleich realisiert ist.

Untersuchung des Self-Biasing-Amplifier und Phasenkomparator II

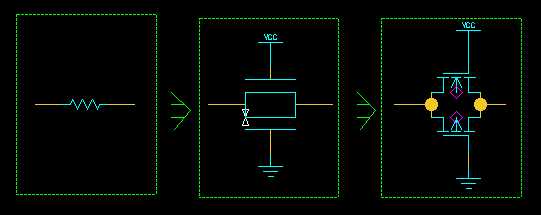

Bild 4 illustriert die Details des Self-Biasing-Amplifier. Dieser

besteht aus sechs CMOS-Inverterstufen, wobei die erste Stufe mittels

eines Widerstandes gegengekoppelt ist. Durch diese

Gegenkopplungsmassnahme regeln sich Ausgang und Eingang der ersten

Inverterstufe auf die halbe Betriebsspannung, wenn der Eingang Pin 14

offen ist oder über einen Kondensator mit einer Signalquelle verbunden

wird. Durch die Gegenkopplung wird erreicht, dass dieser Inverter als

linearer Verstärker arbeiten kann.

Interessant ist das Symbol des Widerstandes R, der mit den beiden

Strichen so ausieht als ob er kapazitiv mit Vcc und GND gekoppelt wäre

und man kann sich fragen wozu dies gut sein soll? Es scheint aber eher,

dass R ein spannungsabhängiger Widerstand ist, denn aus dem Datenblatt

der CMOS-Version CD4046B geht hervor, dass der Eingangwiderstand des

Self-Biasing-Amplifier bei einer Betriebsspannung von 5 VDC einen

Eingangswiderstand von 3 M-Ohm, bei 10 VDC nur 0.7 M-Ohm und bei 15 VDC

nur noch 0.3 M-Ohm hat. MC14046B hat mit 2 M-Ohm bis 0.2 M-Ohm etwas

geringere Werte. Je höher die Vcc-Spannung, um so niedriger diese

Widerstandswerte. Dies deutet darauf hin, dass die Eingangsschaltungen

bei der CMOS- und HCMOS-Version identisch sind und dass es sich bei R um

einen FET handelt, der eben nur als Widerstand arbeitet, aber von der

E-Feldstärke, bzw. von Vcc abhängig ist.

Diese erste Verstärkerstufe arbeitet nur deshalb als linearer

Verstärker, damit es durch ihn möglich ist kleine Spannungsamplituden

symmetrisch um den halben Betriebsspannungswert Vcc/2 zu verstärken, wie

die Datenblätter schliesslich erlauben. Die erste Stufe steuert bei

kleinen Amplitudenwerten noch nicht vollständig aus. Die beiden

Teilbilder in Bild 5 zeigen wie eine Dreieckspannung mit der ersten

Inverterstufe bis zum Clipping begrenzt wird. Die restlichen vier Stufen

sorgen durch die hohe Verstärkung für Vollaussteuerung und hohen

Flankensteilheiten, die den folgenden Komparatorschaltungen als

digitales Signal gerecht werden sollen...

Das obere Teilbild zeigt eine Direktkopplung des Eingangssignals. Dies

ist nur dann erlaubt, wenn das Signal die halbe Betriebsspannung

entsprechend den Daten im Datenblatt unter- und überschreitet. Ist dies

nicht realisierbar oder das Eingangssignal bezieht sich z.B.

amplitudensymmetrisch auf GND, wie dies das untere Teilbild illustriert,

muss man mit einem Kondensator C die DC-Spannung entkoppeln. Dadurch

bleibt am Ein- und Ausgang des ersten Inverters Vcc/2 als

Arbeitspunktspannung erhalten. Durch den Einsatz von C liegt man stets

richtig. Man muss sich gar nicht erst um die Bezugsspannung der

Signalquelle kümmern.

Dass sich die Signale zwischen dem ersten und zweiten Inverter und am

Ausgang des letzten so zeigen, wie abgebildet, ist nicht messbar, weil

diese Anschlüsse am IC nicht zur Verfügung stehen. Man kann bloss den

Schluss daraus ziehen, wenn man annimmt, dass diese CMOS-Inverter sich

ebenso verhalten wie z.B. die Inverter des Hex-Inverter-IC CD4069UB.

Dies ist aber überhaupt nicht sicher, weil die hintereinander

geschalteten Inverter der PLL-Schaltung 4046 bloss einen kleinen

Teil auf dem Chip ausmachen und so die Schaltungsarchitektur kaum exakt

4069-identisch ist und auch die Speisung an diesen Invertern IC-intern

nicht etwa extra kapazitiv abgeblockt ist. Durch die sehr dünnen

Leiterbahnen zeigen sich auch höhere parasitäre Induktivitäten. Dies und

anderes kann dazu führen, dass der gesamte Self-Biasing-Amplifier sich

nicht genau so verhält wie es zu erwarten wäre. Wir werden es noch

erfahren...

Die Testschaltung

Bild 6 zeigt die Testschaltung, welche mit +5 VDC gespiesen wird, mit

dem Self-Biasing-Amplifier und dem Phasen-Komparator II. Man verwendet

dazu am besten einen Funktionsgenerator mit einer fixen

Rechteckausgangsspannung (TTL), die man in der Regel als

Synchronisationssignal verwendet, und einer in Amplitude und Offset

einstellbaren Spannung, umschaltbar auf Sinus, Dreieck und Rechteck. Das

TTL-Synchronisationssignal legt man an COMP.-IN, während das

einstellbare Signal an SIGNAL-IN gelegt wird. Dieses Signal schaltet man

auf Rechteck. Nun beobachtet man mit einem Oszilloskopen die beiden

Signale SIGNAL-IN und PULSE-OUT, wobei die Triggerung auf die

ansteigende Flanke von SIGNAL-IN eingestellt wird. Man stellt die

SIGNAL-IN-Amplitude so ein, wie das mittlere Beispiel illustriert. Die

Impulsmaximalwerte liegen innerhalb der Betriebsspannung. Auf Grund von

Laufzeitverzögerungen, zeigen sich an PULSE-OUT feine negative

Nadelimpulse. Dies ist korrekt und stellt den eingeschwungenen

PLL-Zustand dar. Verschiebt man den Spannungsoffset des

SIGNAL-IN-Impulses so, dass sich seine Maximalwerte entweder ausserhalb

von Vcc (+5V) oder GND befinden, destabilisiert sich zeitweise PULSE-OUT

und wird unbrauchbar. Das selbe gilt, wenn man die Impulsamplitude

soweit erhöht, dass Vcc und GND über- und unterschritten werden. Diese

Störung ist bei der HCMOS-Version eher stärker ausgeprägt als bei der

CMOS-Version. Die Störung kann nicht durch einen zu hohen Strom am

Eingang des Pin 14 verursacht werden, wie man bei Übersteuerung dieses

Einganges annehmen könnte, weil auch ein massiv strombegrenzender

Widerstand in Serie zu diesem Eingang keine Verbesserung bringt.

Ich untersuchte noch den Störfall mit einem Dreiecksignal am Eingang

SIGNAL-IN. Wie bereits bekannt und in Bild 3 illustriert, arbeitet die

PLL-Schaltung nur mit einem Rechtecksignal wirklich stabil. Beobachtet

man auf dem Oszilloskopen PULSE-OUT bei einem niederfrequenten

Dreieicksignal an SIGNAL-IN, zeigt sich ein relativ grosser

Flankenjitter. Womöglich ist dies die Ursache dafür, dass die PLL nur

bei steilen Signalflanken am Eingang des SIGNAL-IN, wie im Falle eines

Rechtecksignales, stabil arbeiten kann.

Die Problemlösung

Es ging um die Realisierung eines 50Hz-netzfrequenzsynchronen

PLL-Frequenzmultiplier mit einer höheren Frequenz zwecks Ansteuerung

einer 50Hz-Notchfilterbank in Switched-Capacitor-Filter-Technik (SC) für

acht Kanäle. In meinem Elektronik-Minikurs

Langzeit-Timer-Schaltungen mit den

Frequenzteilern CD4020B und CD4040B spreche ich in Bild 8 und

zugehöriger Erläuterung den PLL-Frequenzmultiplier kurz an.

Wir befassen uns hier jedoch nur mit dem Problemfall Phasen-Komparator

II, genauer gesagt, mit dem Signaleingang. Die Schaltung war natürlich

schon fixfertig auf einem Print (siehe Titelbild), als ich den Fehler

entdeckte, da er nur spontan in grossen Zeitabständen aufrat. Die

Korrektur war aber einfach. Ich musste eine Leiterbahn auftrennen, einen

SMD-Widerstand und zwei antiparallel geschaltete Silizium-Dioden

einlöten. Diese beiden Dioden arbeiten als Spannungsbegrenzer. So

garantieren sie eine betriebssichere Impulsspannung mit einer Amplitude

von der doppelten Diodenflussspannung von etwa 1.3 Vpp. Seither arbeitet

der PLL-Frequenzmultiplier einwandfrei stabil mit der CMOS- und

HCCMOS-Version des 4046.

Da ich schon vor der Schaltungsdimensionierung wusste, dass der

Self-Biasing-Amplifier nur mit einer Rechteckspannung einwandfrei

arbeitet und PLL-Stabilitaet garantieren kann, realisierte ich mit dem

Timer-IC LMC555 (CMOS-Version) einen Schmitt-Trigger. Man kann ebenso

eine andere Schmitt-Triggerschaltung, z.B. 1/6 des ICs CD4584B

verwenden. Wie es mit dem Timer-IC LMC555 gemacht wird, ist ausführlich

beschrieben in:

Erweiterung: PLL-Problemlösung mit asymmetrischer Speisung

Bei der Betrachtung von Bild 7 stellt sich die Frage wie das Problem

gelöst wird, wenn die Schaltung anstatt mit einer symmetrischen Spannung

von zum Beispiel ±5 VDC mit einer asymmetrischen Spannung von +5 VDC

betrieben wird. Während die HCMOS-Version des PLL-IC 74HC4046 nur mit +5

VDC (+2 VDC bis +6 VDC) betrieben werden kann, eignen sich MC14046B und

CD4046B durchaus für Betriebsspannungen bis +15 VDC. +18 VDC ist

Worstcasegrenze! Bei der Anwendung dieser CMOS-ICs muss man wissen, je

grösser die Betriebsspannung ist, um so besser ist die Störimunität.

Geht man mit der Betriebsspannung allerdings zu nahe an die

Worstcasegrenze, wird die statistische Lebensdauer markant reduziert.

Eine Betriebsspannung von +12 VDC ist vernünftig.

Der Zweck der antiparallel geschalteten Dioden in Bild 7 unten ist es

eine symmetrische stabile Rechteckspannung um den GND-Pegel zu erzeugen,

die garantiert unterhalb der positiven und negativen Betriebsspannung

liegt, aber sicher grösser ist als die minimale Spannung betreffs

Datenblatt. In der positiven Wechselspannungsphase leitet D3 und erzeugt

mit ihrer Durchflussspannung eine Spannung von etwa +0.65 VDC. In der

negativen Wechselspannungsphase sorgt D4 für -0.65 VDC. Es resultiert

die symmetrische Rechteckspannung von etwa 1.3 Vpp. Beim Einsatz der

CMOS-Version und einer Betriebsspannung von 15 VDC, könnnen diese 1.3

Vpp unter Worstcasebetrachtung allerdings knapp werden!

Will man das selbe Prinzip bei einer asymmetrischen Speisung

(Single-Supply-Modus) anwenden, kann man die beiden Dioden nicht mit GND

verbinden. Das Rechtecksignal wäre nicht innerhalb von +Ub und GND.

Siehe dazu Bild 3.3 das zeigt was erlaubt ist. Um den selben Effekt zu

erzielen, müsste man den gemeinsamen Schaltpunkt der beiden Dioden auf

die halbe Betriebsspannung Vcc/2 setzen, was mit zwei zusätzlichen

Widerständen auch realisierbar und überhaupt nicht problematisch wäre.

Allerdings geht es auch einfacher, wie Bild 8 illustriert:

Anstelle der beiden Dioden D3 und D4 in Bild 7 gibt es zwei zusätzliche

Widerstände vor dem Signaleingang Pin 14. Ein Widerstand ist mit Vcc

positiven Betriebsspannung und ein anderer ist mit GND verbunden. Wählt

man alle drei Widerstände R gleich gross, so stellt sich zwischen

Betriebsspannung und GND eine symmetrische Rechteckspannung von einem

Drittel der Betriebsspannung ein. Die Amplitude des Rechtecksignales

passt sich mit dieser Methode stets der Betriebsspannung an.

Der Wert von R ist unkritisch. Er sollte nicht so niedrig sein, dass der

Ausgang des LMC555 unnötig stark belastet wird und nicht so hoch, dass

die Flankensteilheit am Signaleingang des PLL-ICs wegen parasitären

Kapazitäten leidet. Ein Wert von 10 k-Ohm ist bei niedrigen bis

mittleren Frequenzen ein vernünftiger Wert. Bei Anwendungen oberhalb 100

kHz empfiehlt es sich R eventuell niedriger zu wählen.

Netzfrequenzsynchronisation mit unterschiedlicher Gleichrichtung

Wie bei symmetrischer DC-Betriebsspannung die AC-Spannung zur

Netzfrequenzsynchronisation entnommen wird, zeigt Bild 3 in

Schmitt-Trigger mit CMOS-555-Timer... und Bild 7

in diesem Minikurs deutet es an. Mit Bild 9 soll zusätzlich gezeigt

werden, wie es bei asymmetrischer Speisung, also mit nur einer

Speisespannung, gemacht werden muss.

Es gibt zwei Methoden der Vollweggleichrichtung. Die Gleichrichtung im

oberen Schaltbild nennt man Mittelpunktgleichrichterschaltung. Dabei

werden zwei gegenphasige Wechselspannungen einweggleichgerichtet.

Besonders bei niedrigen Spannungen und grossen Strömen bietet diese Art

der Gleichrichtung gegenüber der Brückengleichrichtung den Vorteil des

geringeren Spannungsabfalles und damit geringeren Verlustleistung, weil

bei jeder Phase jeweils nur eine Diode leitet. Nachteilig ist, dass der

Trafo eine Mittelanzapfung oder zwei getrenne Sekundärwicklungen haben

muss. Die Gleichrichtung im unteren Schaltbild nennt man

Brückengleichrichterschaltung. In jeder Phase sind stets zwei Dioden in

Serie leitend. Mehr zum Thema Gleichrichter liest man in den Grundlagen

von Patrick Schnabel:

Betrachten wir in Bild 9 oben die Mittelpunktgleichrichterschaltung,

dann bemerken wir eine Übereinstimmung mit Bild 7. Die für die

Netzsynchronisation benötigte Wechselspannung wird direkt an der

Sekundärspule entnommen. Hier wird einfach zwischen dem einen Spulenende

und dem Mittelpunkt, der mit GND identisch ist, die Wechselspannung

entnommen. Diese Methode eignet sich für eine asymmetrische oder eine

symmetrische Betriebsspannung, also +Ub oder ±Ub. Voraussetzung ist

allerdings die Mittelpunktschaltung.

Im unteren Schalbild mit der Brückengleichrichterschaltung ist die Sache

ein ganz klein wenig komplizierter. Die Wechselspannung wird zwischen

GND des Brückengleichrichters und einer der beiden

Trafo-Sekundäranschlüsse entnommen. Es spielt dabei keine Rolle welchen

Anschluss man benutzt. Wie funktionierts? Nur dann wenn am oberen

Spulenende eine positive Wechselspannungsphase vorliegt, fliesst über R3

ein Strom durch den GND und von diesem über eine

Brückengleichrichterdiode zurück in das untere Spulenende. In R3

erscheint die Spannung einer positiven Sinushalbwelle. Während der

negativen Halbwelle bleibt die Spannung weg, weil durch R3 kein Strom

fliessen kann. Wir haben es mit einer Halbwellengleichrichterschaltung

zu tun. Wozu überhaupt R3? Während der der negativen sperrenden Phase

ist die Einweggleichrichterschaltung hochohmig, was zur Folge hätte,

dass C1 sich nicht entladen könnte. Der LMC555 würde am Ausgang keine

Rechtecksignale liefern. Für die Entladung von C1 sorgen R1 und R3,

wobei R3 wesentlich niederohmiger sein muss als R1.

Spannungsdiagramme am LMC555-Ausgang

Betrachten wir Bild 7 mit seiner symmetrischen Speisung, so fällt auf,

dass die Wechselspannung am Eingang des LMC555 symmetrisch zum GND-Pegel

liegt. Die Hysterese des als Schmitt-Trigger benutzten LMC555 ist

ebenfalls symmetrisch zum GND-Pegel. Dies hat zur Folge, dass das

Ausgangssignal des LMC555 ein Tastverhältnis von 50% hat. Auch das

Tastverhältnis ist also symmetrisch. Illustriert ist dies in Bild 10.1.

Mit Clipping wird gezeigt, dass die Sinusspannung dann beschnitten wird,

wenn dessen Scheitelwerte grösser sind als die positive und negative

Betriebsspannung plus die Diodenflussspannungen der Schutzdioden D1 und

D2 am Eingang des LMC555.

In Bild 9 oben schneidet die Schutzdiode D2 die negative

Sinushalbwelle weg. Der Hysteresemittelwert des LMC555

liegt wegen dessen asymmetrischen Speisung irgendwo innerhalb der

positiven Sinushalbwelle, wie dies Bild 10.2 illustriert. Aus dieser

Asymmetrie resultiert konsequenterweise ein Rechteckausgangssignal mit

ebenfalls asymmetrischem Tastverhältnis (nicht 50%). Der positive

Scheitelwert wird aus dem selben Grund beschnitten, wie im oberen

Abschnitt bereits beschrieben.

In Bild 9 unten liegt an R3, wie bereits beschrieben, eine positive

Halbwellengleichspannung vor. D2 wäre im Prinzip redundant. Ich empfehle

sie trotzdem. Doppelt genäht hält besser. Für diese Dioden eignen sich

die weltbekannten, traditionsreichen und äusserst preiswerten 1N4148

oder 1N914.

Für die vorliegende Anwendung einer PLL-Schaltung ist das Tastverhältnis

dann irrelevant wenn der Phasenkomparator II (siehe die Datenblätter zu

den 4046B) verwendet wird. Dies ist vielleicht die häufigste

PLL-Applikation mit dem 4046

Zum Schluss noch eine kleine Frage...

Mich würde von den Lesern interessieren, wer schon mit dem MC14046B, CD4046B oder 74HC4046 und dem integrierten Phasenkomaparator II eine PLL-Schaltung realisiert hat und es würde mich natürlich zusätzlich sehr interessieren, ob der Anwender mit dem Thema dieses Elektronik-Minikurses konfrontiert wurde. Man möge mir dazu ein paar Zeilen schreiben (E-Mailadresse auf der Indexseite unten).

Anhang 1: Transfer-Gate oder parallelgeschaltete MOS-Feldeffekt-Transistoren

Unterstützung des Lesers: Mathew S.B Neal von Atmel Germany GmbH

Es geht dabei um den zweiten Textabschnitt mit Bild 4 unter dem Kapitel

"Untersuchung des Self-Biasing-Amplifier und Phasenkomparator

II". Herrr Neal schrieb mir, dass hochohmige integrierte Widerstände

in CMOS-ICs in der Regel sogenannte Transfer-Gates sind. Als Alternative

werden manchmal auch parallelgeschaltete MOS-Feldeffekt-Transistoren

verwendet. Beim hier behandelten Self-Biasing-Amplifier wurde ein

Transfer-Gate implementiert.

Das von Herrn Neal beigelegte Bild (siehe unten) illustriert links den

Widerstand, in der Mitte des Bildes das Transfer-Gate und rechts die

parallelgeschalteten MOS-Feldeffekt-Transistoren:

Anhang 2: Vorsicht vor unerwünschter Phasenverschiebung!

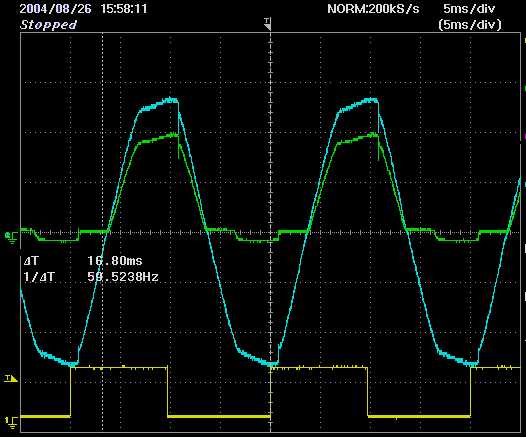

In einer Diskussion im ELKO-Forum machte mich ein Christian

darauf aufmerksam, dass gemäss Bild 9 (unteres Schaltbild) zwischen

dem Ausgang des LMC555 und der Wechselspannung an der Sekundärwicklung

des Trafo eine signifikante Phasenverschiebung auftritt, wie das oben

im Oszillogramm gezeigt wird. Das blaue Diagramm ist diese

Wechselspannung, das grüne ist die Halbwellengleichspannung, gemessen

am Knoten von R1 (100 k-Ohm) und R3 (10 k-Ohm) und das gelbe

Rechtecksignal ist der Ausgang des LMC555.

Es gibt zwei Gründe wie es zu einer Phasenverschiebung kommt:

1. Es ist das passive Tiefpassfilter, bestehend aus R1 und

C1. Die Grenzfrequenz ist mit bloss 22.6 Hz sehr niedrig

gewählt. Hauptgewicht bei einem Projekt war maximale

Störunterdrückung, die Phasenverschiebung war egal. Für viele

Anwendungen genügt jedoch auch eine höhere Grenzfrequenz mit

entsprechend geringerer Phasenverschiebung. Wenn es nur darum geht

allfällig hochfrequente Störimpulse zu unterdrücken, genügt eine

Grenzfrequenz im kHz-Bereich. Wenn es jedoch auch auf eine sehr gute

Unterdrückung von Rundsteuersignalen ankommt, muss man eine niedrige

Grenzfrequenz wählen oder man dimensioniert ein aktives Tiefpassfilter

höherer Ordnung, das exakt eine Phasenverschiebung von 180 Grad

bewirkt. Wie man so etwas macht, zeigt folgender Elektronik-Minikurs:

2. Der mit dem LMC555 aufgebaute Schmitt-Trigger hat

systembedingt eine grosse Hystere. Man konsultiere dazu das

Datenblatt. Wenn man dort die Schaltung anschaut, erkennt man, dass

die Schaltschwellen immer bei 1/3 und 2/3 der Betriebsspannung

betragen. Auch das gibt eine signifikante Phasenverschiebung, die auch

von der Amplitude der Eingangsspannung beim LMC555 abhängig ist.

Diese grosse Hystere hat selbst schon ein hohes Mass an

Störsignalunterdrückung.

Ganz nebenbei, im Kapitel Spannungsdiagramme am LMC555-Ausgang

ist das Thema Phasenverschiebung (Bild 10.1 /10.2) bereits angedeutet...

Thomas Schaerer, 25.01.2001 ; 03.06.2001 ; 08.04.2002 ; 17.07.2002 ; 02.12.2002(dasELKO) ; 14.12.2003 ; 27.08.2004 ; 17.12.2004