# National Semiconductor

# LF13741 Monolithic JFET Input Operational Amplifier

# **General Description**

The LF13741 is a 741 with BI-FET™ input followers on the same die. Familiar operating characteristics—those of a 741—with the added advantage of low input bias current make the LF13741 easy to use. Monolithic fabrication makes this "drop-in-replacement" operational amplifier very economical.

Applications in which the LF13741 excels are those which require low bias current, moderate speed and low cost. A few examples include high impedance transducer amplifiers, photocell amplifiers, buffers for high impedance, slow to moderate speed sources and buffers in sample-and-hold type systems where leakage from the hold capacitor node must be kept to a minimum.

Systems designers can take full advantage of their knowledge of the 741 when designing with the LF13741 to achieve extremely rapid "design times." The LF13741 can also be used in existing sockets to make the "error budget" for input bias and/or offset currents negligible and in many cases eliminate trimming. For higher speed and lower noise use the LF155, LF156, LF157 series of BI-FET operational amplifiers.

- Low input noise current

- 0.01 pA/√Hz

- $5 imes 10^{11}\Omega$

- High input impedanceFamiliar operating characteristics

# **Advantages**

- FET inputs—741 operating characteristics

- Low cost

- Ease of use

- Standard supplies

- Standard pin outs

- Non-rectifying input for RF environment

- Rapid "design time"

# Applications

- Smoke detectors

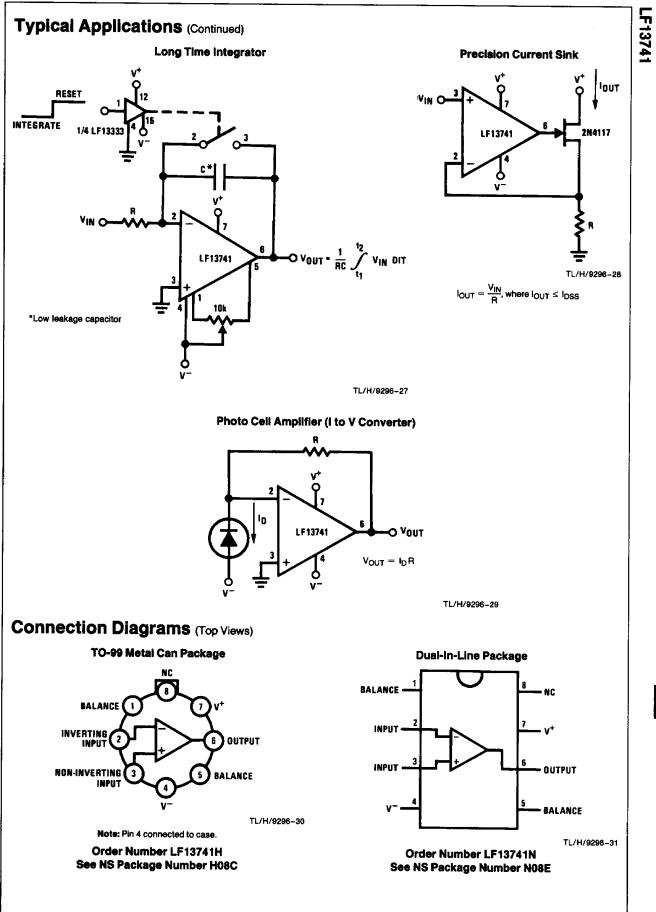

- I to V converters

- High impedance buffers

- Low drift sample and hold circuits

- High input impedance, slow comparators

- Long time timers

- Low drift peak detectors

- Supply current monitors

- Low error budget systems

# Features

(2) O

Low input bias current

50 pA

Input common-mode range to positive supply voltage

# **Simplified Schematic**

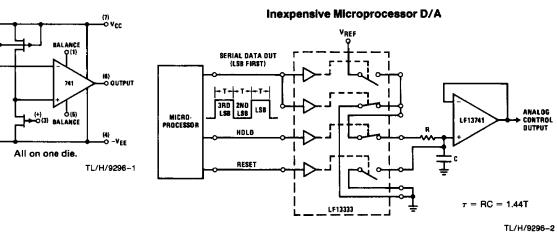

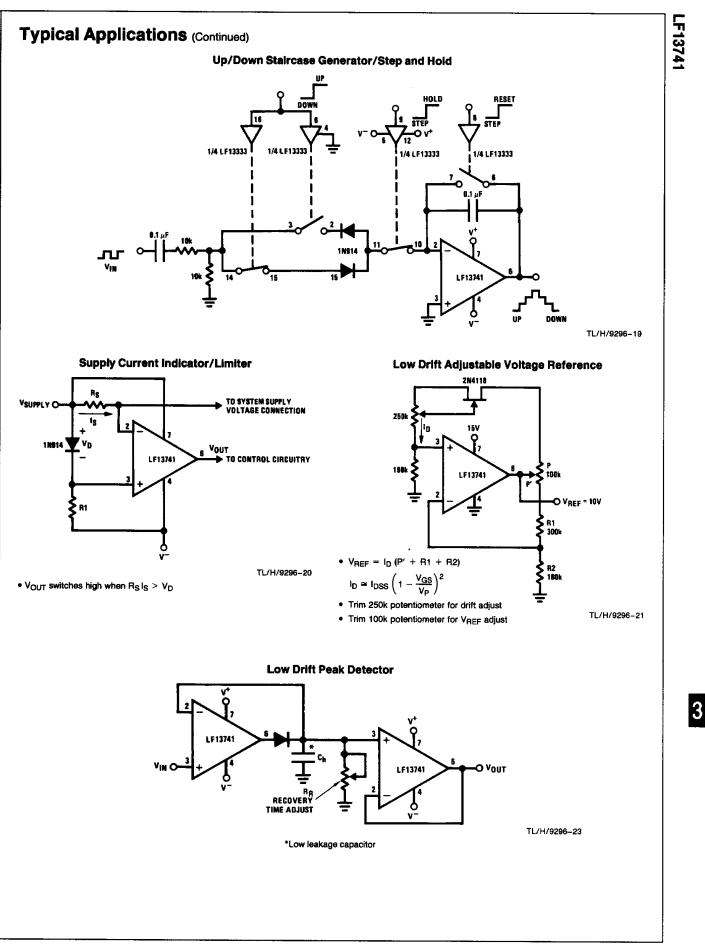

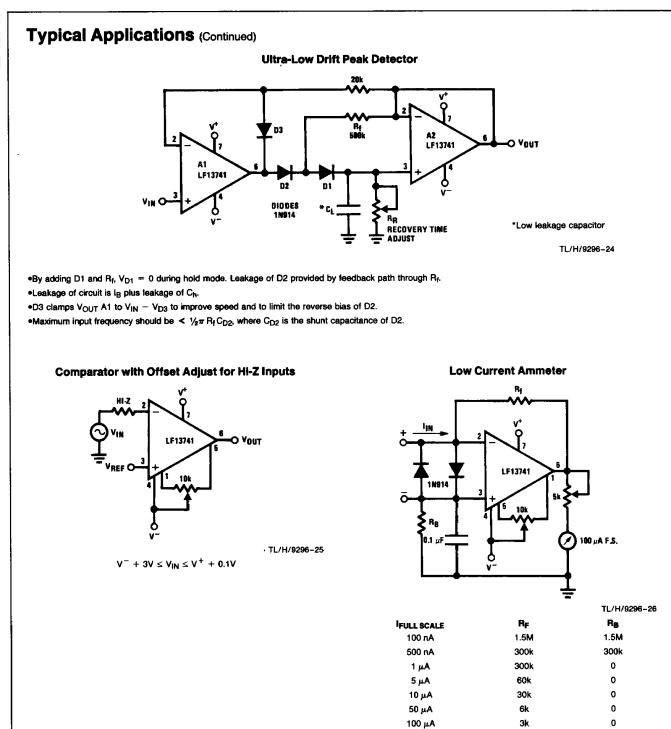

# Typical Applications

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                | ± 18V           |

|-------------------------------|-----------------|

| Operating Temperature Range   | 0°C to +70°C    |

| T <sub>j(MAX)</sub>           | 100°C           |

| Differential Input Voltage    | ± 30V           |

| Input Voltage Range (Note 3)  | ±16V            |

| Output Short Circuit Duration | Continuous      |

| Storage Temperature Range     | -65°C to +150°C |

|                         | H Package      | N Package |

|-------------------------|----------------|-----------|

| $\theta_{iA}$ (Typical) |                |           |

| (Note 1)                | 70°C/W         | 163°C/W   |

| (Note 2)                | 175°C/W        | 218°C/W   |

| $\theta_{jC}$ (Typical) | 25°C/W         |           |

| Metal Package Lead 1    | emperature     |           |

| (Soldering, 10 sec.)    |                | 300°C     |

| Plastic Package (Solde  | ering, 4 sec.) | 260°C     |

| ESD rating to be deter  | rmined.        |           |

# DC Electrical Characteristics (Note 4)

| Symbol                | Parameter                             | Conditions                                    | Min | Тур                  | Max | Units |

|-----------------------|---------------------------------------|-----------------------------------------------|-----|----------------------|-----|-------|

| V <sub>OS</sub>       | Input Offset Voltage                  | $R_S = 10 \text{ k}\Omega, T_A = 25^{\circ}C$ |     | 5                    | 15  | mV    |

|                       |                                       | Over Temperature                              |     |                      | 20  |       |

|                       | Voltage Offset Adjustment<br>Range    |                                               | 10  |                      |     | mV    |

| ΔV <sub>OS</sub> /ΔT  | Average TC of Input Offset<br>Voltage | $R_{S} = 10 k\Omega$                          |     | 10                   |     | μV/°C |

| l <sub>OS</sub>       | Input Offset Current                  | T <sub>j</sub> = 25°C (Notes 4, 5)            |     | 10                   | 50  | pА    |

|                       |                                       | T <sub>j</sub> ≤ 70°C                         |     |                      | 2   | nA    |

| IB                    | Input Bias Current                    | T <sub>j</sub> = 25°C (Notes 4, 5)            |     | 50                   | 200 | pА    |

|                       |                                       | T <sub>j</sub> ≤ 70°C                         |     | 1.6                  | 8   | nA    |

| R <sub>IN</sub>       | Input Resistance                      | T <sub>j</sub> = 25°C                         |     | 5 × 10 <sup>11</sup> |     | Ω     |

| A <sub>VOL</sub> Larg | Large Signal Voltage Gain             |                                               | 25  | 100                  |     | V/mV  |

|                       |                                       | Over Temperature                              | 15  |                      |     | V/mV  |

| Vo                    | Output Voltage Swing                  | $V_{S} = \pm 15V, R_{L} = 10 \text{ k}\Omega$ | ±12 | ±13                  |     | v     |

| V <sub>CM</sub>       | Input Common-Mode Voltage<br>Range    | $V_{S} = \pm 15V$                             | ±11 | + 15.1<br>- 12       |     | v     |

| CMRR                  | Common-Mode Rejection Ratio           | R <sub>S</sub> ≤ 10 kΩ                        | 70  | 90                   |     | dB    |

| PSRR                  | Supply Voltage Rejection Ratio        | (Note 6)                                      | 77  | 96                   |     | dB    |

| ls                    | Supply Current                        |                                               |     | 2                    | 4   | mA    |

3

# AC Electrical Characteristics (Note 4)

| Symbol         | Parameter                      | Conditions                                                        | Min | Тур          | Max | Units            |

|----------------|--------------------------------|-------------------------------------------------------------------|-----|--------------|-----|------------------|

| SR             | Slew Rate                      | V <sub>S</sub> = ±15V, T <sub>A</sub> = 25°C                      |     | 0.5          |     | V/µs             |

| GBW            | Gain-Bandwidth Product         | $V_{S} = \pm 15V, T_{A} = 25^{\circ}C$                            |     | 1.0          |     | MHz              |

| e <sub>n</sub> | Equivalent Input Noise Voltage | $T_A = 25^{\circ}C, R_S = 100\Omega$<br>f = 100 Hz<br>f = 1000 Hz |     | 50<br>37     |     | nV/√Hz<br>nV/√Hz |

| i <sub>n</sub> | Equivalent Input Noise Current | T <sub>j</sub> = 25°C<br>f = 100 Hz<br>f = 1000 Hz                |     | 0.01<br>0.01 |     | pA/√Hz<br>pA/√Hz |

Note 1: The value given is in 400 Linear Feet/Min air flow.

Note 2: The value given is in static air.

Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 4: These specifications apply for V\_S =  $\pm 15V$  and 0°C  $\leq T_A \leq +70$ °C. V<sub>OS</sub>, I<sub>B</sub>, and I<sub>OS</sub> are measured at V<sub>CM</sub> = 0.

Note 5: The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature,  $T_j$ . Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>D</sub>.  $T_j = T_A + \theta_{jA} P_D$  where  $\theta_{jA}$  is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

Note 6: Supply Voltage Rejection Ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice from  $V_S = \pm 10V$  to  $\pm 15V$ .

# LF13741

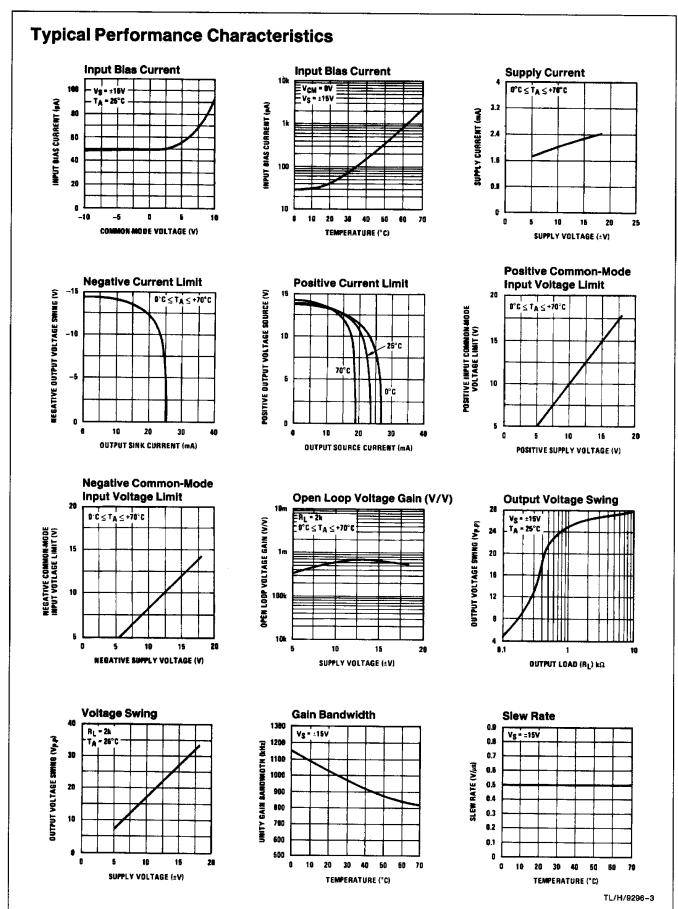

#### Typical Performance Characteristics (Continued) **Common-Mode Rejection Power Supply Rejection Bode Plot** Ratio Ratio 29 120 120 108 (99) COMMON-MODE REJECTION RATIO (48) 15 90 Vs = ±15V VS = ±15V POWER SUPPLY REJECTION RATIO 100 10 80 R\_ = 2k 100 TA = 25°C TA - 25°C 70 5 PHASE (DEGREES) 80 80 ٥ 60 +SUPPLY (GAIN (dB) --5 50 40 30 60 60 -10 111 -15 40 40 PHAS -20 20 Ш --25 10 20 20 --30 0 -36 -10 ٥ ß D.1 18 10 100 1k 19k 100k 10M 10 1 1M 100 1k 100k 10k 110 FREQUENCY (MHz) FREQUENCY (Hz) FREQUENCY (Hz) **Undistorted Output Equivalent Input** Voltage Swing **Noise Voltage Output Impedance** EQUIVALENT INPUT NOISE VOLTAGE (nV//Hz) 24 140 1k V<sub>S</sub> = ±15V R<sub>L</sub> = 2k T<sub>A</sub> = 25°C A<sub>V</sub> = 1 = ±15V ٧g 21 OUTPUT VOLTAGE SWING (VP.P) 120 ┼┠┽┠╫ 25°C 18 **OUTPUT IMPEDANCE (**(2) 100 190 15 <1% 01\$1 190 80 12 18 60 9 40 6 3 20 0 ٥ 0.1 1k 10 108 1k 10k 100 16 10k 10k 1006 110 180 1N FREQUENCY (Hz) FREQUENCY (Hz) FREQUENCY (Hz) TL/H/9296-4 LF13741 Pulse Responses

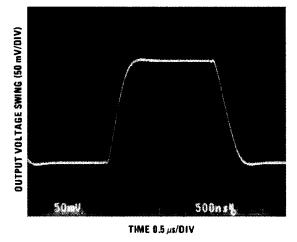

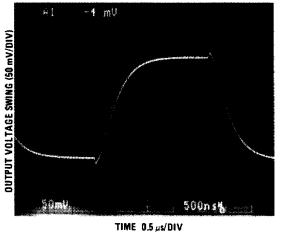

Small Signal Non-Inverting Pulse Response

A<sub>V</sub> = +1(Follower)

TL/H/9296-5

Small Signal Inverting Pulse Response

# Typical Performance Characteristics (Continued)

### LF13741 Pulse Responses (Continued)

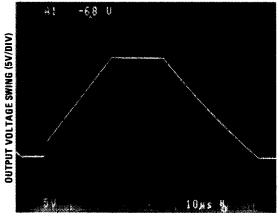

Large Signal Non-Inverting Pulse Response

TIME 10 µs/DIV

TL/H/9296-7

# Application Hints

#### **GENERAL CHARACTERISTICS**

The LF13741 makes the job of converting from a bipolar to an FET input op amp easy. As a systems designer you are probably very familiar with the operating characteristics of a 741 op amp. In fact, many of you have used 741s with FET input followers—that's just what the LF13741 is, but it's all on a single die.

When you need a low cost, reliable, well known op amp with low input currents and moderate speed, use an LF13741.

#### DIFFERENTIAL INPUTS

You don't have to use clamps across the inputs for differential input voltages of less than 40V. The input JFETs of the LF13741, in addition to being well matched, have large reverse breakdown voltages from gate to source and drain.

#### POSITIVE INPUT COMMON-MODE VOLTAGE LIMIT

With the LF13741 (unlike the normal 741) you can take both inputs above the positive supply voltage by more than 0.1V before the amplifier ceases to function. This feature enables you to use the LF13741 to monitor and/or limit the current from the same supply used to power it (see typical applications).

If you exceed the positive common-mode voltage limit on only one input, the output phase will remain correct. When you exceed the limit on both inputs, the output phase is unpredictable.

#### NEGATIVE INPUT COMMON-MODE VOLTAGE LIMIT

- There are two negative input voltage ranges of interest:

- 1. The range between the negative common-mode voltage limit and the negative supply voltage.

- 2. Voltages which are more negative than the negative supply voltage.

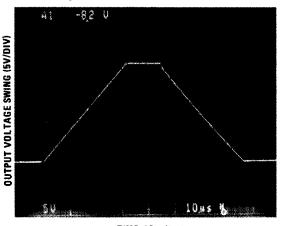

Large Signal Inverting Pulse Response

TIME 10 µs/DIV

TL/H/9296-8

\_F13741

If you take only one of the inputs of the LF13741 into the first range, the output phase will remain correct. When you take both inputs into this range the output will go toward the positive supply voltage.

If you force either or both of the inputs into the second range, an internal diode will be turned "ON." Unless you externally limit the diode current to about 1 mA, the device will be destroyed. In either case, limited or unlimited input current, you cannot predict the output.

#### HANDLING

You do not have to take any special precautions in handling the LF13741. It has JFET, as opposed to fragile MOSFET, inputs.

#### APPLYING POWER

You should never: reverse the power supplies to the LF13741; plug a part in backwards in a powered socket or board; make the negative supply voltage more positive than an input voltage.

Any one of these supply conditions will forward bias an internal diode. If you have not externally limited the resulting current, the device will be destroyed.

#### LAYOUT

To ensure stability of response you should take care with lead dress, component placement and power supply decoupling. For example, the body of feedback resistors (from output to input pins) should be placed close to the inverting input pin. Noise "pickup" and capacitance to ground from the input pin will be minimized—effects which are usually desirable.

Because of the very low input bias currents of the LF13741, special care should be taken in printed circuit board layouts to prevent unnecessary leakage from the input nodes, (see Typical Applications).

# Application Hints (Continued)

#### FEEDBACK POLE

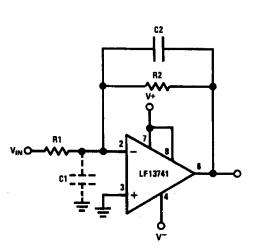

You create a feedback pole when you place resistive feedback around an amplifier. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and there is negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3 dB frequency (a distinct possibility when using FET op amps), you should place a lead capacitor from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant (*Figure 1*).

TL/H/9296-9

Parasitic input capacitance C1  $\simeq$  (3 pF for LF13741 plus any additional layout capacitance) interacts with feedback elements and creates undesirable high frequency pole. To compensate, add C2 such that: R2C2  $\simeq$  R1C1. FIGURE 1

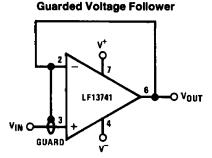

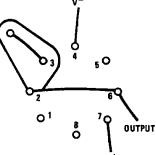

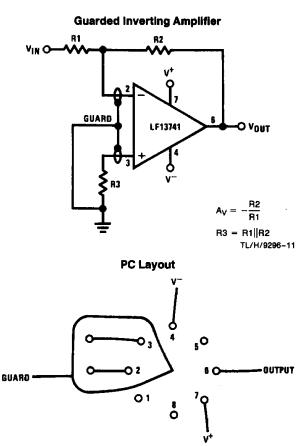

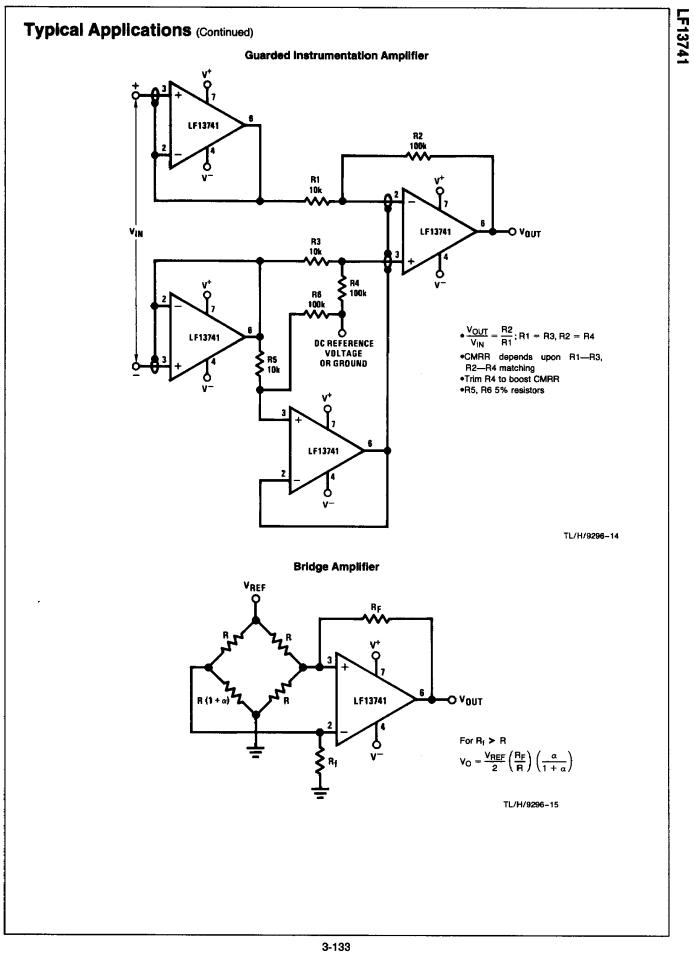

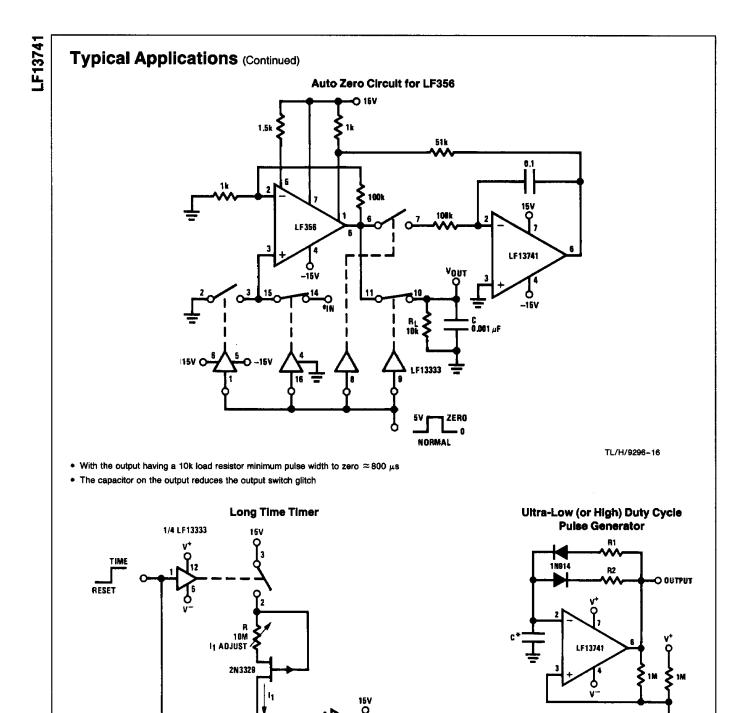

# Typical Applications (Continued)

Circuits Using Guard Rings to Prevent Leakage Currents Between Inputs and V-

TL/H/9296-10

TL/H/9296-12

TL/H/9296-13

\* Low leakage capacitor

TL/H/9296-18

114

• toutput HIGH

$$\approx$$

R1C  $l$  n  $\frac{4.8 - 2V_S}{4.8 - V_S}$

• toutput LOW  $\approx$  R2C  $l$  n  $\frac{2V_S - 7.8}{V_S - 7.8}$

where  $V_S = V^+ + |V^-|$

• Time =  $\frac{C1}{I_1}$  VTHRESHOLD

Output goes high on time out

· Reverse op amp inputs for output low on time out

1/4 LF13333

15

14

C1 low leakage capacitor

6

O OUTPUT

TL/H/9296-17

LF13741

Q

VTHRESHOLD TIME ADJUST 100k

.C1 100 μF

LF13741

3-137

3

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

http://www.ti.com/corp/docs/investor\_relations/pr\_09\_23\_2011\_national\_semiconductor.html

This file is the datasheet for the following electronic components:

LF13741 - http://www.ti.com/product/lf13741?HQS=TI-null-null-dscatalog-df-pf-null-wwe LF13741H - http://www.ti.com/product/lf13741h?HQS=TI-null-null-dscatalog-df-pf-null-wwe LF13741N - http://www.ti.com/product/lf13741n?HQS=TI-null-null-dscatalog-df-pf-null-wwe LF13741N - http://www.ti.com/product/lf13741n?HQS=TI-null-null-dscatalog-df-pf-null-wwe LF13741H - http://www.ti.com/product/lf13741h?HQS=TI-null-null-dscatalog-df-pf-null-wwe LF13741H - http://www.ti.com/product/lf13741h?HQS=TI-null-null-dscatalog-df-pf-null-wwe